近日有媒体报道称,中芯国际将在本月试产7nm芯片,并争取在今年10月份实现量产。其次,中芯国际在14nm制程工艺良品率已追上台积电,达到业界水平的90%-95%。

值得一提的是,此次中芯国际试产7nm芯片是计划通过DUV工艺来试产。

7nm 制程工艺如何实现?

按常规经验,一般将28nm芯片加工能力作为分界线——超过28nm属于成熟工艺芯片,低于28nm则可归为先进工艺芯片。先进工艺里面的14nm,中芯国际也已经实现了真正意义上的量产,并且已经获得了稳定的客户源,算是在“先进工艺芯片站住了一只脚”。但在7nm芯片加工领域,当前的中芯国际依然只是取得了阶段性成果。

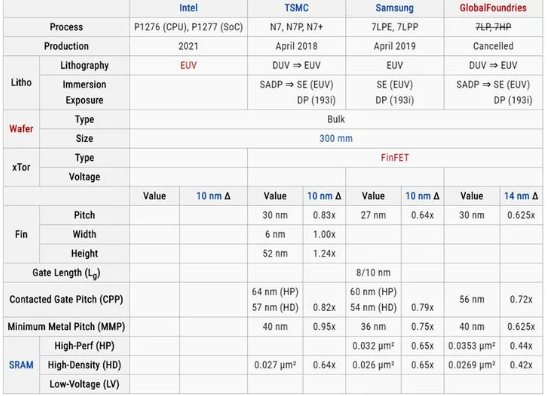

基本算是获得了初步加工能力,但仍未能完全实现大规模商品化,即处于“向大批量商业化生产冲击阶段”——按中芯国际CEO梁孟松的说法,在其带领下已经攻克到了7nm技术,并准备今年4月份试产,顺利的话在今年年底或明年初的时候可以批量生产。那么7nm 制程工艺到底该如何实现呢?首先我们看一下7nm 工艺制程的特征尺寸和工艺参数,找出其中最小的特征尺寸,比如 fin width 6nm, fin pitch 27/30nm,gate length 8/10nm,minimum metal pitch 36/40nm,gate pitch 54/57nm,我们需要考虑的问题就是如何通过光刻工艺来实现这些特征尺寸。 7nm Node目前可以实现7nm 制程的只有台积电和三星两家,三星是从一开始就使用EUV光刻机来实现,而台积电则是从DUV开始实现,然后再转向EUV 。也就是说,目前7nm 制程工艺使用DUV 和 EUV 都是可以实现的,

7nm Node目前可以实现7nm 制程的只有台积电和三星两家,三星是从一开始就使用EUV光刻机来实现,而台积电则是从DUV开始实现,然后再转向EUV 。也就是说,目前7nm 制程工艺使用DUV 和 EUV 都是可以实现的,

台积电的初代的7nm工艺,就完全由DUV光刻机实现。相对于台积电的上一代主要工艺节点16nm,7nm可以提供3.3倍的电路密度。相同功耗,可以提供35·40%的性能提升。如果基于相同的性能做比较,功耗可降低65%,非常可观。 后来,台积电基于初代7nm工艺,在生产步骤上进行了优化,推出了一个改进版本。叫做7nm性能增强版(7nm Performance-enhanced version,n7p), 性能有所提升,约7%。在引入EUV光刻机之后,首次应用在7nm的一些步骤的改进上。一些在DUV光刻机下需要多次曝光才能够完成的图形,由于EUV的引入,可以一次完成。这样做的好处就是能够减少多次曝光所引入的不可控的畸变,从而提升芯片的一致性和良率。引入EUV的7nm,被命名为N7plus。根据台积电方面的数据,n7plus和初代n7工艺相比,电路密度提升1.2倍,相同功耗情况下,性能可提升10%。相同性能下,功耗可降低15%。这些就是台积电DUV和EUV在7nm工艺的差异。

如何用134 nm的光源做成7nm芯片?

目前国际上已经实现7nm芯片生产的半导体厂商基本都是采用EUV光刻机来生产,但由于中国半导体企业缺乏这类先进的光刻机,因此中芯国际只能通过DUV光刻机来实现其量产7nm芯片的目标。

Q1中芯国际宣布和阿斯麦签订的批量采购协议,期限从原来的2018年1月1日至2020年12月31日延长至2021年12月31日,同时中芯国际在未来12个月内就购买生产晶圆的阿斯麦产品与后者签订买单,总计约12亿美元。阿斯麦发布公告澄清称,这份采购包主要与DUV(深紫外线)光刻技术的现有协议相关。

值得一提的是,阿斯麦DUV产品分为三种ArFi,ArF和KrF,如果中芯国际采购的是最先进的ArFi产品,则暗示中芯生产7nm芯片克服了最大一个障碍。ArFi产品也是阿斯麦20Q4卖得最好的产品。中芯国际Q1向阿斯麦订的12亿美元DUV产品是不是ArFi光刻机,还未得知。

那如何用DUV光刻机制造工艺尺寸更小的芯片?

假定是ArFi产品,如果要用134 nm的光源刻出更细的线条,这还需要更多的技术支持。

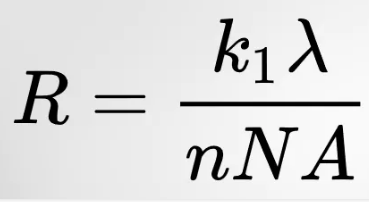

我们可以通过这个公式来大致看一下134nm的光源能刻出的工艺分辨率,其中:R,分辨率,比如90nm、65nm、45nm之类。λ,激光的波长,现在业界已经从248nm过渡到了现在最常用的134nm,还有更为先进的13.5nm。n,为介质折射率,空气约1,水约1.44。NA,为数值孔径,和镜子大小,以及距离有关。k1,系统常数,代指掩膜等相关技术。

所以通过这个公式我们可以大致计算出,在一般情况下134nm波长的光源分辨率也就能做到40nm左右。那么接下来的问题就是如何突破这个所谓的“一般情况”了。对此业界大体有两种解决办法:浸润式光刻和多重曝光。浸入式光刻技术是在2000年初首先由麻省理工学院林肯实验室亚微米技术小组提出,他们认为在传统光刻机的光学镜头与晶圆之间的介质可用水替代空气,以缩短曝光光源波长和增大镜头的数值孔径,从而提高分辨率。水与空气的折射率之比为1.44:1如果用水替代空气,相当于134nm波长缩短到93nm,如果采用比水介质反射率更高的其液体,可获得比93nm更短的波长。简单来说就是运用了惠更斯原理,让光从一种介质折射进入另一种介质,那么在分界点相当于一个波源,向外发散子波。也就是说在这个过程中光的波长发生了改变,通过这种方式我们获得了一个波长更小的光源。 ▲一种多重曝光的流程示意图

▲一种多重曝光的流程示意图

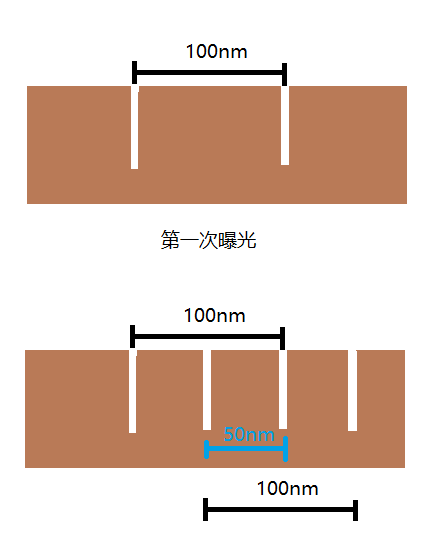

另外一种技术就是多重曝光了,在图中最上面是已经经过一次Patterning的保护层(绿色,如SiN)再加上一层光刻胶(蓝色)。光刻胶在新的Mask下被刻出另一组凹槽(中间)。最后光刻胶层被去掉,留下可以进一步蚀刻的结构。

简单来说就是将本应一次曝光的图形分成两次甚至更多次曝光来制作。比如要刻几条等间距的线,单次曝光可能只能刻出间距100nm的线,那么这时候稍微再移动大概50nm再刻一次,这时候线与线的间距就变成50nm了。

当然除了浸润式光刻和多重曝光,还有很多技术可以帮助进一步减小半导体制造工艺中的关键尺寸。但是比起用各种技术优化,直接更换光源会有较大的提升,即从波长为134nm的DUV光刻机换成波长大致为13.5nm的EUV光刻机。

总结

就目前而言,能够量产7nm以及7nm芯片的企业,只有台积电和三星,即便是英特尔,也不能自主生产制造7nm芯片,可能要延迟到2022年。这意味着,一旦中芯在4月份成功风险试产7nm芯片,其就会成为全球第三家掌握7nm芯片制造技术的企业。

据了解,台积电用DUV光刻机量产7nm芯片,采用的是多次曝光,至于中芯采用什么办法试产7nm芯片,暂时还不得而知。但中芯已经规模量产了N+1工艺的芯片,用梁孟松的话说,N+1工艺的芯片,其逻辑面积与台积电7nm芯片相当,仅仅是性能提升不足。

也就是说,中芯在7nm芯片制造上,可能会采用多次曝光,也可能会采用类似N+1工艺,准确消息只能等中芯对外公布了。

最后,虽然美国企业已经获得了向中芯出售14nm以及14nm以上芯片所需要的设备、技术等,但7nm等更先进制程的芯片,则依旧受限。也就是说,即便是中芯在4月份成功试产7nm芯片,掌握了7nm芯片的制造技术,如果得不到相关设备、原材料等,中芯7nm芯片的产能也将是有限的。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。