本文主要源于几篇产业报告,从中提取了一些相对重要且客观信息进行梳理。文中图表较多,可能会影响阅读,其实整体思路很简单,主要分为四个板块:1、AI时代的内存墙问题;2、HBM用来解决这个问题并阐述了HBM的概念及技术特点;3、HBM的制造工艺;4、HBM的核心材料。

AI算力时代的内存墙问题

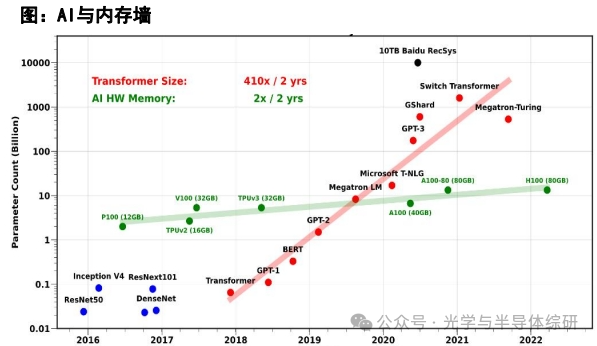

随着摩尔定律的不断迭代,CPU运行速度快速提升,CPU主频高达5GHz,而DRAM内存性能取决于电容充放电速度以及DRAM与CPU之间的接口带宽,存储性能提升远慢于CPU,DRAM内存带宽成为制约计算机性能发展的重要瓶颈。DDR4内存主频为2666~3200MHz,带宽为6.4GB/s,但是在AI应用中(高性能计算/数据中心),算力芯片的数据吞吐量峰值在TB/s级,主流的DRAM内存或显存带宽一般为几GB/s到几十GB/s量级,与算力芯片存在显著的差距,“内存墙”由此形成。以Transformer类模型为例,模型大小平均每两年翻410倍,AI硬件上的内存大小仅仅是以每年翻2倍的速率在增长;内存墙问题不仅与内存容量大小有关,也包括内存的传输带宽;内存容量和传输的速度都大大落后于硬件的计算能力。

典型的DRAM中,每个芯片有八个DQ引脚(数据传输路径,用作处理器和存储器之间通信的数据总线,必须具备读写功能,所以具备双向特性),即数据输入/输出引脚。组成DIMM模块单元后(双列直插式存储模块,安装在PCB板上的存储模块,包含多个存储芯片,被用作PC或者服务器中的主存储单元),共有64个DQ引脚。随着数据处理速度等方面的要求不断提高,数据传输量也不断增加,传统DRAM DQ引脚的数量已无法保证数据快速通过。传统DRAM需要大量空间与CPU/GPU等处理器通信,同时封装的形式看需要通过引线键合或PCB进行连接,DRAM不可能对海量数据进行并行处理。

HBM的概念

HBM(High Bandwidth Memory)意为高带宽存储器,是一种面向需要极高吞吐量的数据密集型应用程序的DRAM,HBM 的作用类似于数据的“中转站”,就是将使用的每一帧,每一幅图像等图像数据保存到帧缓存区中,等待GPU 调用。

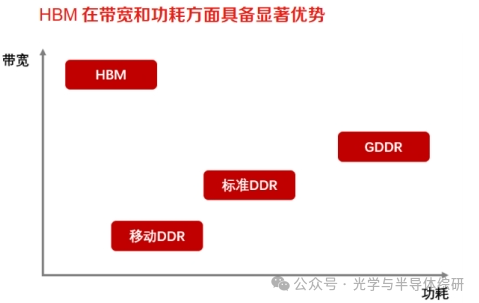

HBM 在带宽、功耗、封装体积方面具备明显优势。按照不同应用场景,行业标准组织 JEDEC 将DRAM 分为三个类型:标准 DDR、移动 DDR 以及图形 DDR,图形 DDR 中包括 GDDR 和 HBM。相比于标准的 DDR4、DDR5 等产品,以 GDDR 和 HBM 为代表的图形 DDR 具备更高的带宽,其中HBM 在实现更大带宽的同时也具备更小的功耗和封装尺寸。

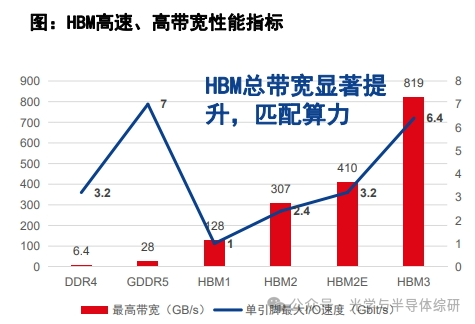

HBM 有效解决了内存墙的问题,在中高端 GPU 中得到广泛应用。高带宽存储器HBM(Highband Memory)使用硅通孔TSV和微凸块技术垂直堆叠多个DRAM可以显著提升数据处理速度,性能提升的同时尺寸有所减少。2013年开始,JEDEC制定了高带宽存储器系列标准(包括HBM,HBM2,HBM2E,HBM3),其中,HBM3相比2代标准有显著的提升,芯片单个引脚速率达到6.4Gbit/s,总带宽超过1TB/s。

HBM的技术特点

主要可分为高速/高带宽;更低功耗;扩展容量

高速/高带宽:HBM2E和HBM3的单引脚最大输入/输出(I/O)速度分别达3.2Gbit/s和6.4Gbit/s,低于GDDR5存储器的7Gbit/s,但HBM的堆栈方式可通过更多的I/O数量使总带宽远高于GDDR5,例如HBM2带宽可以达到307 GB/s。海力士官网数据显示:HBM3E的数据处理速度,相当于可以在1s内下载230部全高清(FHD)级电影(每部5千兆字节,5GB),优化后可用于处理人工智能领域的海量数据。

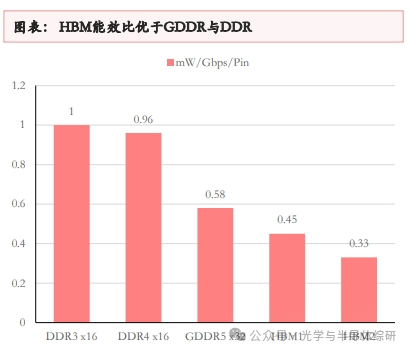

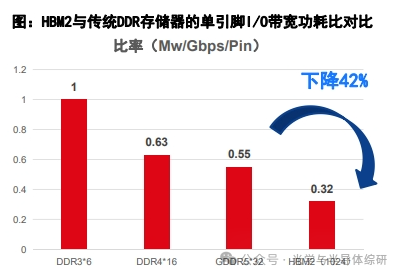

更低功耗:采用微凸块和TSV技术,存储和算力芯片信号传输路径短,单引脚I/O速率较低,使HBM具备更好的内存功耗能效特性。以DDR3存储器单引脚I/O带宽功耗为基准,HBM2的I/O功耗比明显低于DDR3/DDR4和GDDR5,相比于GDDR5存储器,HBM2的单引脚I/O带宽功耗比数值降低42%。

HBM制造工艺

HBM 制造工艺包括 TSV、Bumping 和堆叠等工艺环节。HBM 是由多个 DRAMdie 堆叠而成,利用硅通孔(TSV)和微凸块(Microbump)将 die 之间相连接,多层 DRAMdie 再与最下层的 Basedie 连接,然后通过凸块(Bump)与硅中阶层(interposer)互联。HBM 与 GPU、CPU 或 ASIC 共同铺设在硅中阶层上,通过 CoWoS 等 2.5D/3D 封装工艺相互连接,硅中介层通过 CuBump 连接至封装基板(Package Substrate)上,最后封装基板再通过锡球与下方的PCB 基板相连。

HBM工艺流程中所需要的设备清单如下:

HBM堆叠核心:MR-MUF(向上堆叠方式)

SK海力士表示,通过先进的MR-MUF堆叠技术加强了工艺效率和产品性能的稳定性;随着对高速高容量的需求不断增加,散热问题预计将成为HBM产品持续迭代的重大技术障碍。MR-MUF:将半导体芯片堆叠后,为了保护芯片和芯片之间的电路,在其空间中注入液体形态的保护材斜,并固化的封装工艺技术。与每堆叠一个芯片铺上薄膜型材料的方式对比,工艺效率高,散热方面也更有效。具体步骤:1)连接芯片的微凸块采用金属塑封材料;2)一次性融化所有的微凸块,连接芯片与电路;3)芯片与芯片之间或者芯片与载板之间的间隙填充,绝缘和塑封同时完成。

HBM堆叠技术发展趋势

海力士正在加速开发新工艺“混合键合”,截止目前,HBM的DRAM芯片之间通过“微凸块”材料进行连接,通过混合键合,芯片可以在没有凸块的情况下连接,从而显著减小芯片的厚度。当间距小到20um以内,热压键合过程中细微倾斜使得钎料变形挤出而发生桥连短路,难以进一步缩减互联间距。HBM芯片标准厚度为720um,预计2026年左右量产的第六代HBM4需要纵向垂直堆叠16层DRAM芯片,当前的封装技术很难让客户满意,所以混合键合的应用被认为是必然的趋势。2023年海力士用于第三代HBM产品(HBM2e)测试混合键合技术,规格低于HBM4产品。同时海力士拟计划将新一代的HBM与逻辑芯片堆叠在一起,取消硅中介层。

混合键合的定义:混合键合是一种永久键合,将介电键合(siox)与嵌入式金属(Cu)结合起来互联,形成电介质和金属-金属键。使用紧密嵌入电介质中的微小铜焊盘可以提供比铜微凸块多1000倍的I/O连接。支持3D封装和先进的存储立方体更高的互连密度。混合键合可以实现低于10um的键合间距,当接近10u尺寸时带有焊锡尖端的铜凸块会遇到可靠性问题,从而导致转向混合键合。

新一代HBM材料-LMC

根据《我国集成电路材料专题系列报告》,超90%的集成电路采用环氧塑封料(Epoxy Molding Compound,简称EMC)作为包封材料。环氧塑封料可分为饼状、片状、颗粒状(GMC)和液态(LMC)四种。其中,饼状环氧塑封料主要用于传统封装,采用传递成型法对芯片实现包封;后三者主要用于先进封装。片状、GMC和LMC采用压缩法实现芯片包封。其中GMC具有操作简单、工时较短、成本较低等优势;LMC具备可中低温固化、低吸水率以及高可靠性等优点。LMC可应用于HBM封装中。SK海力士在其HBM3产品上采用了MR-MUF(Mass Reflow-Molded Underfil)技术,大幅提高了散热性能。然而,相比固态EMC,LMC填料含量低。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。