SK海力士:HBM5将转向3D封装及混合键合技术!

9月3日,SK 海力士封装(PKG)研发副社长李康旭(Kangwook Lee)在SEMICON Taiwan 2024上以“准备AI 时代的HBM和先进封装技术”为题,分享了SK 海力士最新的HBM技术。

9月3日,SK 海力士封装(PKG)研发副社长李康旭(Kangwook Lee)在SEMICON Taiwan 2024上以“准备AI 时代的HBM和先进封装技术”为题,分享了SK 海力士最新的HBM技术。

SK海力士的HBM规划

李康旭指出, HBM 是克服“存储墙”(Memory Walls)的最优解决方案,基于其强大的I/O 并行化能力,使HBM 成为Al 系统中用于训练和推理的最高规格DRAM。

根据应用产品(Application)不同,使用的HBM数量也不同。随着HBM技术的发展,在训练和推理AI 服务器中搭载HBM 平均数量也会增加,如近期训练服务器应用需要8 个HBM3E,推理则只需要4-5 个,长远估算可能分别要12 个和8 个HBM4 /HBM4E。

李康旭表示,SK 海力士计划在2025 年推出12 层的HBM4 产品,通过自家研发的封装技术,在HBM 产品的能效和散热性能上更具竞争力。

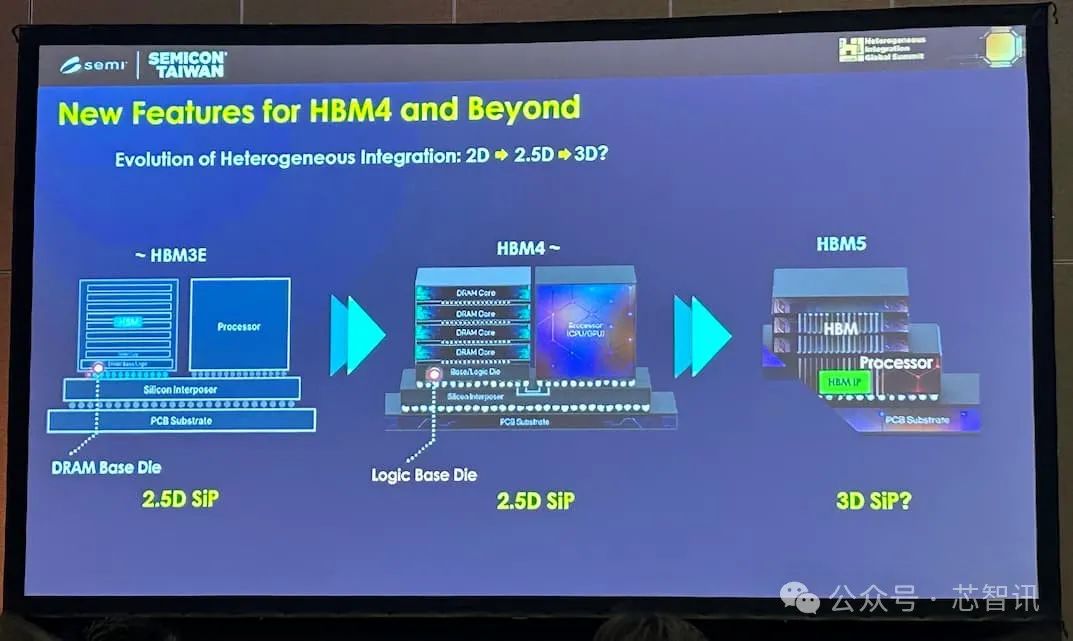

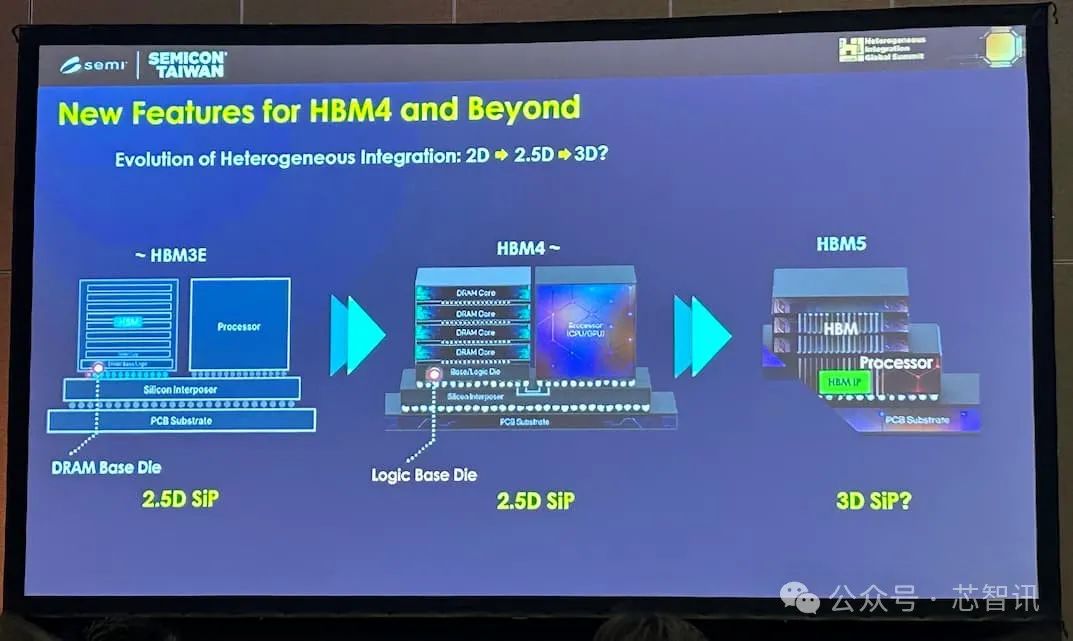

有趣的是,SK 海力士到HBM3E 仍是DRAM 基础裸片(Base Die),采用2.5D 系统级封装,到HBM4 考虑将DRAM Base Die 改成Logic Base Die,使性能和能效获得进一步提升。此外,到了HBM5 架构可能再次改变,SK 海力士目前正评估包括2.5D 和3D 系统级封装(SiP)在内的各种方案。

提到未来HBM 技术挑战,李康旭表示在封装、设计面临许多挑战,以封装来说是堆叠数限制,更希望直接结合逻辑芯片和HBM 堆叠,客户目前也对3D SIP 感兴趣,因此3D SIP、存储芯片带宽、结合客户需求和协作,都是未来挑战之一。对于一些新创AI芯片公司出于成本考虑,采用增大片上SRAM来减少对于HBM的依赖的做法,李康旭认为,这主要仍取决于产品应用,有些公司宣称HBM 太贵,所以找寻其他不需要HBM 的解决方案,但仍需要看具体情况,高性能计算产品仍需要HBM ,但某些应用可能不需要有HBM,主要仍取决于应用场景。

提到未来HBM 技术挑战,李康旭表示在封装、设计面临许多挑战,以封装来说是堆叠数限制,更希望直接结合逻辑芯片和HBM 堆叠,客户目前也对3D SIP 感兴趣,因此3D SIP、存储芯片带宽、结合客户需求和协作,都是未来挑战之一。对于一些新创AI芯片公司出于成本考虑,采用增大片上SRAM来减少对于HBM的依赖的做法,李康旭认为,这主要仍取决于产品应用,有些公司宣称HBM 太贵,所以找寻其他不需要HBM 的解决方案,但仍需要看具体情况,高性能计算产品仍需要HBM ,但某些应用可能不需要有HBM,主要仍取决于应用场景。

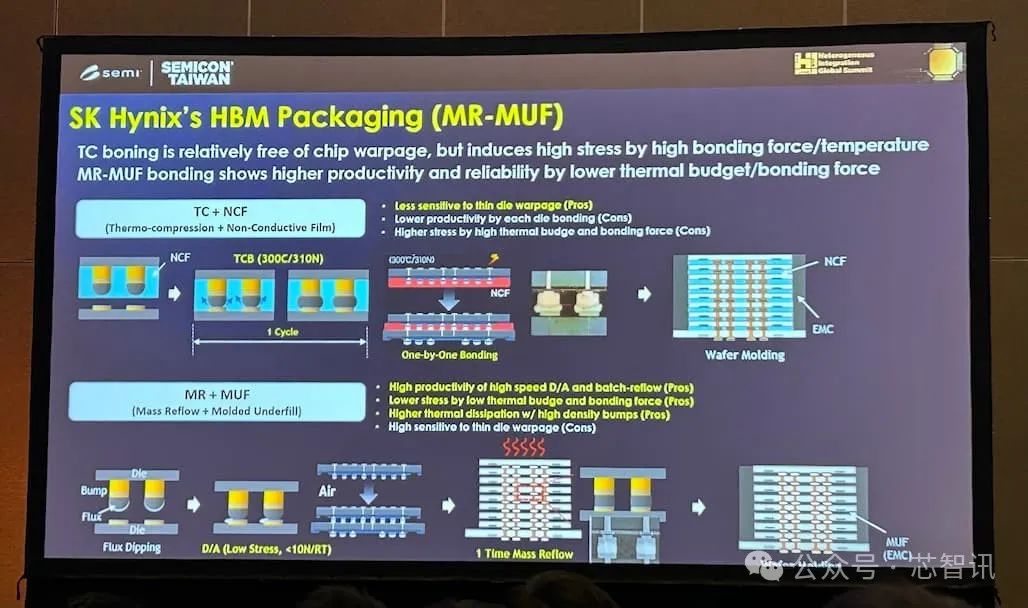

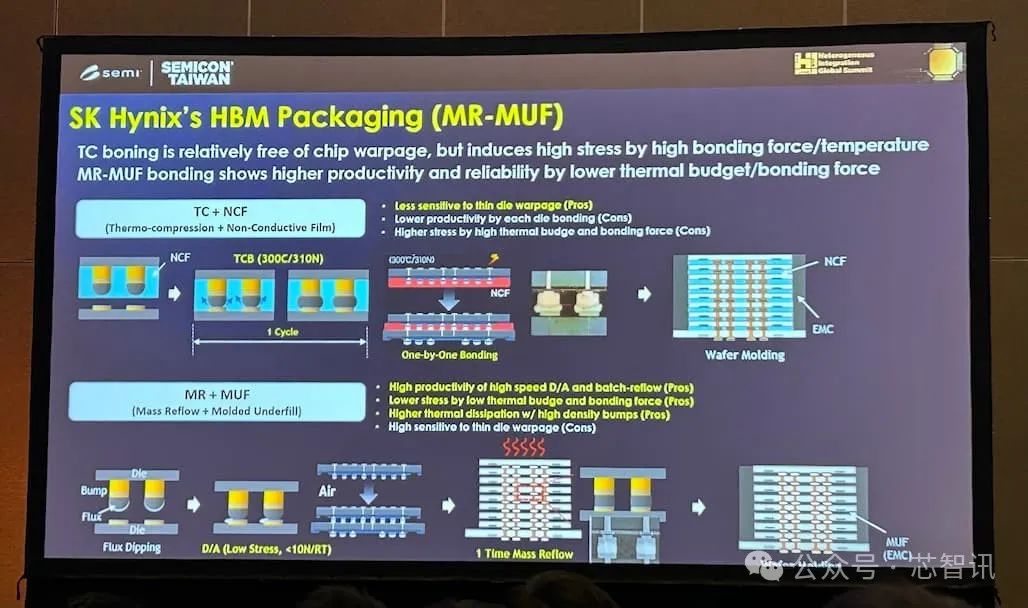

两种封装路线:MR-MUF 和Hybrid BondingSK 海力士目前的HBM 产品主要采用MR-MUF 封装技术,具有低压、低温键合和批量热处理的优势,在生产效率和可靠性优于TC-NCF 制程。此外,具有高热导特性的Gap-Fill 材料(填充空隙的材料)和高密度金属凸块(在垂直堆叠HBM DRAM时起连接电路作用的微小鼓包型材料)的形成,散热可比TC-NCF 制程有36% 性能优势。 但是由于堆叠将面临高度限制,目前SK 海力士不断找寻新方法,在有限高度下塞入更多堆叠层数。李康旭指出,公司8 层HBM3/HBM3E 使用MR-MUF技术;12层HBM3/HBM3E 将采用Advanced MR-MUF技术;明年下半年准备出货的12 层HBM4 同样采Advanced MR-MUF 技术;至于后续的16 层HBM4/ HBM4E 将同步采用Advanced MR-MUF 和混合键合(Hybrid Bonding)两种技术,未来堆叠20 层以上产品(如HBM5)则将转向Hybrid Bonding 前进。

但是由于堆叠将面临高度限制,目前SK 海力士不断找寻新方法,在有限高度下塞入更多堆叠层数。李康旭指出,公司8 层HBM3/HBM3E 使用MR-MUF技术;12层HBM3/HBM3E 将采用Advanced MR-MUF技术;明年下半年准备出货的12 层HBM4 同样采Advanced MR-MUF 技术;至于后续的16 层HBM4/ HBM4E 将同步采用Advanced MR-MUF 和混合键合(Hybrid Bonding)两种技术,未来堆叠20 层以上产品(如HBM5)则将转向Hybrid Bonding 前进。 李康旭指出,SK海力士目前正在研发16 层产品相关技术,最近确认对16 层产品仍可适用Advanced MR-MUF技术的可能性。此外,SK海力士此前也表示,从HBM4E 开始会更强调“定制化HBM”,以应对各种客户需求,如提升芯片效率。

李康旭指出,SK海力士目前正在研发16 层产品相关技术,最近确认对16 层产品仍可适用Advanced MR-MUF技术的可能性。此外,SK海力士此前也表示,从HBM4E 开始会更强调“定制化HBM”,以应对各种客户需求,如提升芯片效率。

李康旭解释,标准HBM 和定制化HBM 核心芯片相同,但是Base Die(基础芯片)不同,主要是再加入客户的IP,芯片效率也可能更高。

另据韩媒报道,SK 海力士将小芯片技术(chiplet)导入存储控制器(memory controller)。对此,李康旭表示目前控制器是在单芯片(SoC)中,但未来会针对小芯片封装技术,结合存储控制器。除了HBM 外,SSD 的SoC 控制器也会采用这项技术。

来源:芯智讯

--End--

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。

提到未来HBM 技术挑战,李康旭表示在封装、设计面临许多挑战,以封装来说是堆叠数限制,更希望直接结合逻辑芯片和HBM 堆叠,客户目前也对3D SIP 感兴趣,因此3D SIP、存储芯片带宽、结合客户需求和协作,都是未来挑战之一。

提到未来HBM 技术挑战,李康旭表示在封装、设计面临许多挑战,以封装来说是堆叠数限制,更希望直接结合逻辑芯片和HBM 堆叠,客户目前也对3D SIP 感兴趣,因此3D SIP、存储芯片带宽、结合客户需求和协作,都是未来挑战之一。